OOPS! You forgot to upload swfobject.js ! You must upload this file for your form to work.

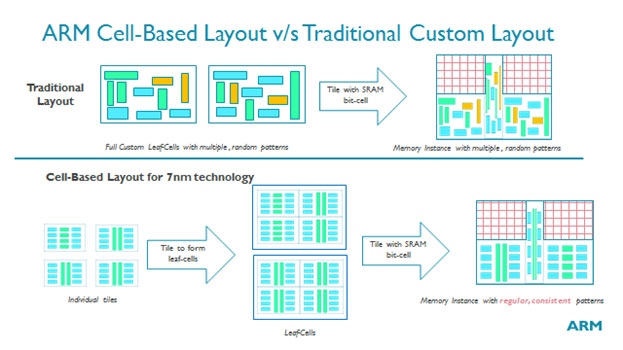

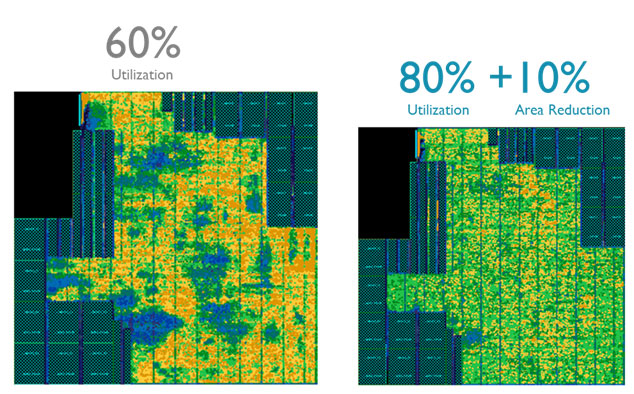

ARM support for 7-nm process technology TSMC package for designers

![]()

|

xtreview is your : Video card - cpu - memory - Hard drive - power supply unit source |

|

|||

|

|

||||

Recommended : Free unlimited image hosting with image editor

Recommended : Free unlimited image hosting with image editor

|

xtreview is your : Video card - cpu - memory - Hard drive - power supply unit source |

|

|

|

|

||

|

Xtreview Support  N-Post:xxxx Xtreview Support        |

ARM SUPPORT FOR 7-NM PROCESS TECHNOLOGY TSMC PACKAGE FOR DESIGNERS |

| Please Feel Free to write any Comment; Thanks  |

Xbox One will get keyboard and mouse support (2017-09-05)

Toshiba intends to expand memory production without WDC support (2017-08-04)

Support for AMD Bristol Ridge hybrid processors appeared in CPU-Z (2017-07-12)

NVIDIA is increasingly convincing about support for DirectX 12 graphics processors Fermi (2017-07-06)

EA and BioWare are going to support Anthem for ten years (2017-06-20)

Intel chipsets will support USB 3.1 and Wi-Fi only in 2018 (2017-06-17)

Crypto currency fever supported the stock price AMD (2017-06-08)

Apple HomePod home column with Siri support (2017-06-07)

In the struggle for Toshiba assets, Foxconn secured the support of Apple and Amazon (2017-06-06)

AMD AGESA v1.0.0.6 update will support memory up to DDR4-4000 (2017-05-26)

Intel promises to endow the future processors with Thunderbolt 3 support (2017-05-25)

Supercomputer based on NVIDIA Volta will support PCI Express 4.0 (2017-05-22)

AMD representatives could not support the share price of the company (2017-05-18)

Open BenchTable open stands now offer support for installation on the side (2017-05-07)

The release of Colony add-on for Halo Wars 2 was postponed due to a broken support unit (2017-04-24)

TC U will receive a dustproof and waterproof case and support for two SIM-cards (2017-04-18)

Intels chipsets for Coffee Lake will offer native support for USB 3.1 (2017-04-17)

GPU-Z utility improves support for AMD Radeon RX 5xx series video cards (2017-04-15)

Published the first patches for Linux with support for Intel Cannonlake CPU (2017-04-08)

Support for Radeon RX 580-570 and 16-core AMD Ryzen processors appeared in AIDA64 (2017-04-06)

![]()

To figure out your best laptops .Welcome to XTreview.com. Here u can find a complete computer hardware guide and laptop rating .More than 500 reviews of modern PC to understand the basic architecture

7600gt review

7600gt is the middle card range.

We already benchmarked this video card and found that ...

geforce 8800gtx and 8800gts

geforce 8800gtx and 8800gts  Xtreview software download Section

Xtreview software download Section  AMD TURION 64 X2 REVIEW

AMD TURION 64 X2 REVIEW  INTEL PENTIUM D 920 , INTEL PENTIUM D 930

INTEL PENTIUM D 920 , INTEL PENTIUM D 930  6800XT REVIEW

6800XT REVIEW  computer hardware REVIEW

computer hardware REVIEW  INTEL CONROE CORE DUO 2 REVIEW VS AMD AM2

INTEL CONROE CORE DUO 2 REVIEW VS AMD AM2  INTEL PENTIUM D 805 INTEL D805

INTEL PENTIUM D 805 INTEL D805  Free desktop wallpaper

Free desktop wallpaper  online fighting game

online fighting game  Xtreview price comparison center

Xtreview price comparison center Lastest 15 Reviews

Rss Feeds

Last News

- The new version of GPU-Z finally kills the belief in the miracle of Vega transformation

- The motherboard manufacturer confirms the characteristics of the processors Coffee Lake

- We are looking for copper coolers on NVIDIA Volta computing accelerators

- Unofficially about Intels plans to release 300-series chipset

- The Japanese representation of AMD offered monetary compensation to the first buyers of Ryzen Threadripper

- This year will not be released more than 45 million motherboards

- TSMC denies the presentation of charges from the antimonopoly authorities

- Radeon RX Vega 64 at frequencies 1802-1000 MHz updated the record GPUPI 1B

- AMD itself would like to believe that mobile processors Ryzen have already been released

- AMD Vega 20 will find application in accelerating computations

- Pre-orders for new iPhone start next week

- Radeon RX Vega 57, 58 and 59: the wonders of transformation

- ASML starts commercial delivery of EUV-scanners

- The older Skylake processors with a free multiplier are removed from production

- Meizu will release Android-smartphone based on Helio P40

- AMD Bristol Ridge processors are also available in American retail

- The fate of Toshiba Memory can be solved to the next environment

- duo GeForce GTX 1080 Ti in GPUPI 1B at frequencies of 2480-10320 MHz

- New Kentsfield overclocking record up to 5204 MHz

- Lenovo released Android-smartphone K8

HALO 3 HALO 3 - Final Fight!

PREY Prey is something you don t often see anymore: a totally unigue shooter experience.

computer news computer parts review Old Forum Downloads New Forum Login Join Articles terms Hardware blog Sitemap Get Freebies