# Product Change Notification 107746 - 00

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications. Intel may make changes to specifications and product descriptions at any time, without notice.

Should you have any issues with the timeline or content of this change, please contact the Intel Representative(s) for your geographic location listed below. No response from customers will be deemed as acceptance of the change and the change will be implemented pursuant to the key milestones set forth in this attached PCN.

Americas Contact: asmo.pcn@intel.com

Asia Pacific Contact: apacgccb@intel.com

Europe Email: eccb@intel.com

Japan Email: jccb.ijkk@intel.com

Copyright  $\odot$  Intel Corporation 2007. Other names and brands may be claimed as the property of others.

Celeron, Centrino, Intel, the Intel logo, Intel Core, Intel NetBurst, Intel NetMerge, Intel NetStructure, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel Viiv, Intel XScale, Itanium, MMX, Paragon, PDCharm, Pentium, and Xeon are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

Learn how to use Intel Trade Marks and Brands correctly at <a href="http://www.intel.com/intel/legal/tmusage2.htm">http://www.intel.com/intel/legal/tmusage2.htm</a>.

# **Product Change Notification**

Change Notification #: 107746- 00

Change Title: Boxed Intel® Core<sup>TM</sup>2 Duo Desktop

Processor E4400, PCN 107746-00, Product Design, L-2 to M-0 Stepping Conversion

Date of Publication: Jul 19, 2007

#### **Key Characteristics of the Change:**

Product Design

### **Forecasted Key Milestones:**

| Date Customer Must be Ready to Receive Post-Conversion Material: | Aug 13, 2007 |

|------------------------------------------------------------------|--------------|

| Date of First Availability of Post-Conversion Material:          | Aug 13, 2007 |

The date of "First Availability of Post-Conversion Material" is the projected date that a customer may expect to receive the Post-Conversion Materials. This date is determined by the projected depletion of inventory at the time of the PCN publication. The depletion of inventory may be impacted by fluctuating supply and demand, therefore, although customers should be prepared to receive the Post-Converted Materials on this date, Intel will continue to ship and customers may continue to receive the pre-converted materials until the inventory has been depleted.

#### **Description of Change to the Customer:**

The boxed Intel® Core<sup>TM</sup>2 Duo desktop processor E4400 will undergo the following changes for the L-2 to M-0 stepping conversion:

- New S-Spec and Material Master Number for the converting product

- CPUID will change from 6F2 to 6FD

- The Electrical and Mechanical Specifications remain within the current specifications. Intel anticipates no changes to customer platforms designed to previous Intel guidelines

- Thermal specification has changed:

- o Extended HALT power specification will reduce from 12 Watts to 8 Watts

- o Maximum allowed Case Temperature will increase from 61.4°C to 73.2°C

- o Tcontrol offset will remain the same relative to 0 with the increase in maximum allowed Case Temperature, which will help reduce acoustics

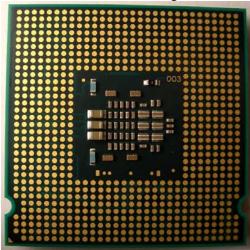

- Minor visible difference between the L-2 and M-0 packages (see below for a visual comparison).

- o While the packages are visually different, the M-0 package is pin-compatible with the L-2 package and Intel anticipates no changes to customer platforms designed to Intel guidelines.

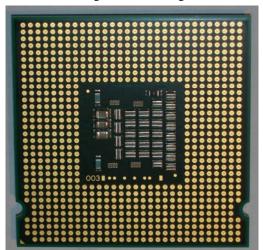

Original L-2 Package

#### **Customer Impact of Change and Recommended Action:**

Minimal re-qualification and/or validation is expected for the M-0 stepping conversion due to no feature set changes between the L-2 and M-0 steppings.

Refer to Intel® Core<sup>TM</sup>2 Extreme Processor X6800 and Intel® Core<sup>TM</sup>2 Duo Desktop Processor E6000 and E4000 Sequence Electrical, Mechanical, and Thermal Specifications (EMTS).

The boxed Intel® Core<sup>TM</sup>2 Duo desktop processor E4400 M-0 stepping will require a BIOS update. Once customers implement the BIOS update, they will be able to accept both L-2 stepping material and M-0 stepping material. Customers should be ready to receive a combination of both L-2 stepping material and M-0 stepping material by the "Date Customer Must be Ready to Receive Post-Conversion Material" above.

## **Products Affected / Intel Ordering Codes:**

| Processor# |          | Pre Conversion<br>Product Code | Pre<br>Conversion |        | Post Conversion<br>Product Code | Post<br>Conversion | Post<br>Conversion |

|------------|----------|--------------------------------|-------------------|--------|---------------------------------|--------------------|--------------------|

|            |          |                                | S-Spec            | MM#    |                                 | S-Spec             | MM#                |

| E4400      | 2.00G 2M | BX80557E4400                   | SLA3F             | 889015 | BX80557E4400                    | SLA98              | 892087             |

|            | 800      |                                |                   |        |                                 |                    |                    |

#### **Reference Documents / Attachments:**

Document: Location #:

**PCN Revision History:**

Date of Revision: Revision Number: Reason:

Jul 19, 2007 Originally Published PCN