OOPS! You forgot to upload swfobject.js ! You must upload this file for your form to work.

In the new architecture of processors, Intel abandoned the internal ring bus

![]()

|

xtreview is your : Video card - cpu - memory - Hard drive - power supply unit source |

|

|||

|

|

||||

Recommended : Free unlimited image hosting with image editor

Recommended : Free unlimited image hosting with image editor

|

POSTER: computer news || IN THE NEW ARCHITECTURE OF PROCESSORS, INTEL ABANDONED THE INTERNAL RING BUS |

DATE:2017-06-16 |

|

|

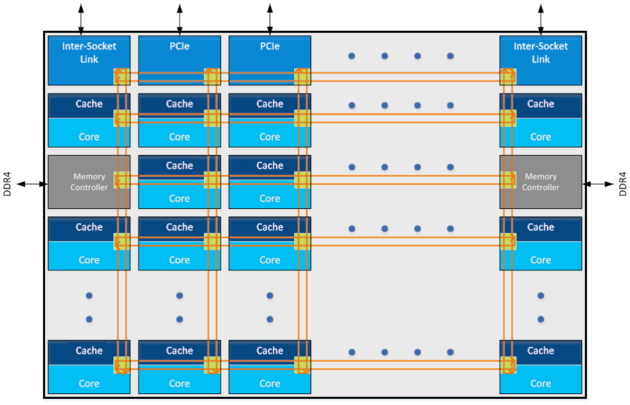

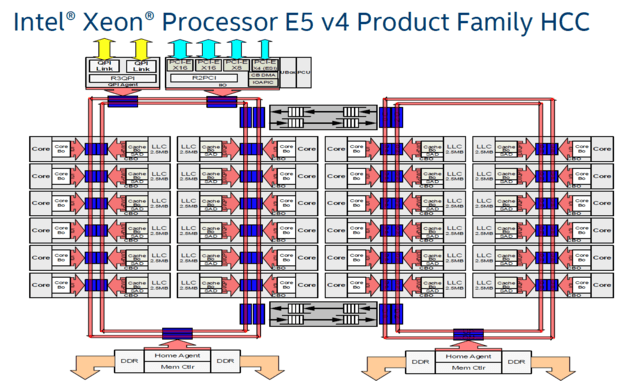

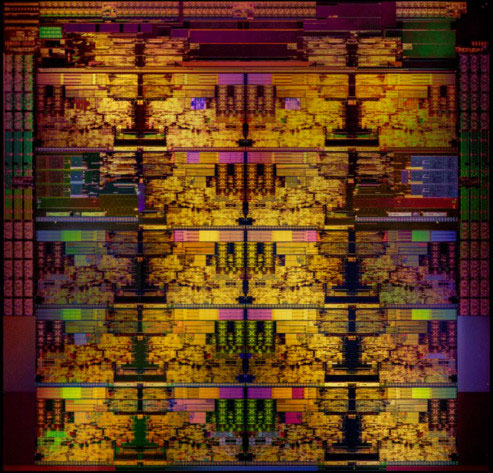

In March, Intel showed an image of a 28-core crystal processor Skylake-SP. Then we noticed that the location of the cores and interfaces has undergone significant changes. Yesterday at Intel at one of the home events explained what these design changes are related to. As it turned out, in the future Intel will refuse (and has already refused for Skylake processors in versions of Xeon and desktop solutions of higher performance) from the internal processor ring bus.  The ring bus was introduced in 2008 together with the Nehalem architecture and the Westmere-EX processors. It was necessary in connection with the increase in the number of core on the crystal. The developers of Intel used three variants of the design of the processors (depending on the maximum number of cores on the chip) with three variants of the ring bus. In the most difficult case, the processor inside was divided into two clusters, each of which was serviced by two ring buses. Between each other, the buses were connected by bi-directional switches with buffering (in the diagram above they are indicated in gray). As the number of core increases, the ring bus has become an obstacle to increasing the capacity and reducing delays. More precisely, it has become too much to consume, so that it can be scaled in the direction of increasing the speed of data exchange. Therefore, in the Skylake-SP processors, Intel developers decided to use a different structure for connecting the cores to each other - a well-tested cellular network in the Intel Xeon Phi (Knights Landing) architecture.

Each core in the new architecture has its own switch with a buffer and is connected to any other core within the processor only through two nodes - outgoing and incoming. This allows the mesh bus to operate at relatively low frequencies and significantly reduce the total interface consumption without degrading bandwidth and increasing latency. In addition, this communication structure scales very well, allowing Intel to increase the number of cores on the chip in the future without a noticeable increase in the energy costs for internal data transport.  Clarifying the essence of the new internal bus, as well as the appearance of the image of the 18-core processor with a new design, also makes it possible to ensure that the new processors do carry an integrated 6-channel memory controller, which is now spread around the edges on the crystal just above the middle.

Related Products : | ||

|

|

||

|

xtreview is your : Video card - cpu - memory - Hard drive - power supply unit source |

|

|

|

|

||

|

Xtreview Support  N-Post:xxxx Xtreview Support        |

IN THE NEW ARCHITECTURE OF PROCESSORS, INTEL ABANDONED THE INTERNAL RING BUS |

| Please Feel Free to write any Comment; Thanks  |

The new version of GPU-Z finally kills the belief in the miracle of Vega transformation (2017-09-08)

We are looking for copper coolers on NVIDIA Volta computing accelerators (2017-09-08)

Unofficially about Intels plans to release 300-series chipset (2017-09-08)

AMD Vega 20 will find application in accelerating computations (2017-09-08)

AMD Bristol Ridge processors are also available in American retail (2017-09-07)

duo GeForce GTX 1080 Ti in GPUPI 1B at frequencies of 2480-10320 MHz (2017-09-07)

New Kentsfield overclocking record up to 5204 MHz (2017-09-07)

Advertising Radeon RX 570 for 279 dollars AMD caused a storm of emotions (2017-09-07)

The European Court sent Intel case on abuses for reconsideration (2017-09-07)

Huawei overtook Apple and became the second largest smartphone manufacturer in the world (2017-09-07)

Twelve-core Core i9-7920X lost the lid in front of the photographic lens (2017-09-06)

In exchange for increasing the stake in the joint venture with Toshiba, Western Digital Corporation is ready to refuse to participate in the auction (2017-09-06)

China banned the creation of new ICO crypto-currency and ordered to return the money for the created one (2017-09-06)

The six-core processor Intel Coffee Lake lit up at a Chinese auction (2017-09-06)

Budget Android-smartphone Xiaomi certified in China (2017-09-06)

Delivery of virtual reality seats Roto VR will begin in late October (2017-09-05)

Compact systems Intel NUC based on Coffee Lake will be released in the second quarter of 2018 (2017-09-05)

Asustek increases its share in the segment of expensive motherboards (2017-09-05)

Ilon Mask believes that the third world war can begin artificial intelligence (2017-09-05)

The six-core processor Intel Coffee Lake has conquered the frequency of 5.0 GHz (2017-09-05)

![]()

To figure out your best laptops .Welcome to XTreview.com. Here u can find a complete computer hardware guide and laptop rating .More than 500 reviews of modern PC to understand the basic architecture

7600gt review

7600gt is the middle card range.

We already benchmarked this video card and found that ...

geforce 8800gtx and 8800gts

geforce 8800gtx and 8800gts  Xtreview software download Section

Xtreview software download Section  AMD TURION 64 X2 REVIEW

AMD TURION 64 X2 REVIEW  INTEL PENTIUM D 920 , INTEL PENTIUM D 930

INTEL PENTIUM D 920 , INTEL PENTIUM D 930  6800XT REVIEW

6800XT REVIEW  computer hardware REVIEW

computer hardware REVIEW  INTEL CONROE CORE DUO 2 REVIEW VS AMD AM2

INTEL CONROE CORE DUO 2 REVIEW VS AMD AM2  INTEL PENTIUM D 805 INTEL D805

INTEL PENTIUM D 805 INTEL D805  Free desktop wallpaper

Free desktop wallpaper  online fighting game

online fighting game  Xtreview price comparison center

Xtreview price comparison center Lastest 15 Reviews

Rss Feeds

Last News

- The new version of GPU-Z finally kills the belief in the miracle of Vega transformation

- The motherboard manufacturer confirms the characteristics of the processors Coffee Lake

- We are looking for copper coolers on NVIDIA Volta computing accelerators

- Unofficially about Intels plans to release 300-series chipset

- The Japanese representation of AMD offered monetary compensation to the first buyers of Ryzen Threadripper

- This year will not be released more than 45 million motherboards

- TSMC denies the presentation of charges from the antimonopoly authorities

- Radeon RX Vega 64 at frequencies 1802-1000 MHz updated the record GPUPI 1B

- AMD itself would like to believe that mobile processors Ryzen have already been released

- AMD Vega 20 will find application in accelerating computations

- Pre-orders for new iPhone start next week

- Radeon RX Vega 57, 58 and 59: the wonders of transformation

- ASML starts commercial delivery of EUV-scanners

- The older Skylake processors with a free multiplier are removed from production

- Meizu will release Android-smartphone based on Helio P40

- AMD Bristol Ridge processors are also available in American retail

- The fate of Toshiba Memory can be solved to the next environment

- duo GeForce GTX 1080 Ti in GPUPI 1B at frequencies of 2480-10320 MHz

- New Kentsfield overclocking record up to 5204 MHz

- Lenovo released Android-smartphone K8

HALO 3 HALO 3 - Final Fight!

PREY Prey is something you don t often see anymore: a totally unigue shooter experience.

computer news computer parts review Old Forum Downloads New Forum Login Join Articles terms Hardware blog Sitemap Get Freebies