OOPS! You forgot to upload swfobject.js ! You must upload this file for your form to work.

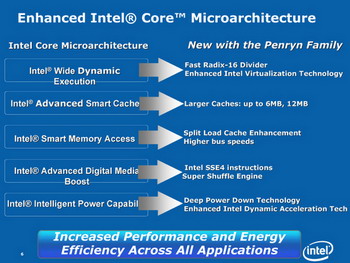

Penryn 8 times faster with GPU

![]()

|

xtreview is your : Video card - cpu - memory - Hard drive - power supply unit source |

|

|||

|

|

||||

Recommended : Free unlimited image hosting with image editor

Recommended : Free unlimited image hosting with image editor

|

POSTER: Zaarco || PENRYN 8 TIMES FASTER WITH GPU |

DATE:2007-05-24 |

|

|

Stephen Fischer, chief Intel Penryn architect revealed that one of 47 new SSE4 instructions embarked on the next Intel architecture, will be able to accelerate 8 times the bandwidth between CPU and GPU. Thanks to this instruction, MOVNTDQA, CPU can load 64 bytes data packages from memory, instead of 16 bytes. Moreover, these batches are not stored in the traditional CPU cache levels 1, 2 or 3, they are transferred in dedicated plugs. This make system save transactions, FSB bandwidth and increase transfer effectiveness. A similar instruction had already been introduced with the SSE2 for the opposite exchanges, when data coming from peripheral must be written in main memory. But which relationship with a graphics board do you wonder? Eh well, this kind of writings and readings of many consecutive data is usually met within the framework exchanges between CPU and GPU, when each one access the frame buffer, i.e data forming image. This kind of optimizations will not bring notable results before many months, but, referred to the current context (Larrabee, AMD Fusion) we can note Intel effort to CPU and GPU fusion. | ||

|

|

||

|

xtreview is your : Video card - cpu - memory - Hard drive - power supply unit source |

|

|

|

|

||

|

Xtreview Support  N-Post:xxxx Xtreview Support        |

PENRYN 8 TIMES FASTER WITH GPU |

| Please Feel Free to write any Comment; Thanks  |

Radeon RX Vega 64 at frequencies 1802-1000 MHz updated the record GPUPI 1B (2017-09-08)

Radeon RX Vega 57, 58 and 59: the wonders of transformation (2017-09-07)

duo GeForce GTX 1080 Ti in GPUPI 1B at frequencies of 2480-10320 MHz (2017-09-07)

Lenovo released Android-smartphone K8 (2017-09-07)

Eighteen-core Core i9-7980XE overclocked to 5.0 GHz (2017-09-06)

Qualcomm does not plan to release Snapdragon 836 (2017-09-06)

Radeon R9 280 new records (2017-09-06)

Lenovo K8 Note with a dual camera and a 4000 mAh battery (2017-09-06)

Compact systems Intel NUC based on Coffee Lake will be released in the second quarter of 2018 (2017-09-05)

The GeForce GTX 1080 Ti at the frequencies 2657-10008 MHz took the third place in GPUPI 1B (2017-09-04)

Xiaomi Mi 7 based on Snapdragon 845 (2017-09-04)

The length of the video card GeForce GTX 1080 in the Gigabyte version does not exceed 169 mm (2017-09-04)

MediaTek announces 8-core 16-nm mobile chips Helio P23 and Helio P30 (2017-08-30)

Samsung expects to sell more than 11 million Android-smartphones Galaxy Note 8 (2017-08-29)

Samsung Galaxy Tab 8.0 2017 will be launched as Galaxy Tab A2 S (2017-08-28)

IPhone 8 will cost a minimum of 999 dollars (2017-08-28)

Intel Core i7-8700K seen in the companys motherboard ASRock Z370 Pro4 (2017-08-26)

Tesla trunking tractor will not exceed 480 km on electric traction without recharging (2017-08-25)

Expansion of 10-nm Intel processors range will be on 2018 (2017-08-24)

Leaks on the performance of Intel Core i3-8350K Coffee Lake (2017-08-24)

![]()

To figure out your best laptops .Welcome to XTreview.com. Here u can find a complete computer hardware guide and laptop rating .More than 500 reviews of modern PC to understand the basic architecture

7600gt review

7600gt is the middle card range.

We already benchmarked this video card and found that ...

geforce 8800gtx and 8800gts

geforce 8800gtx and 8800gts  Xtreview software download Section

Xtreview software download Section  AMD TURION 64 X2 REVIEW

AMD TURION 64 X2 REVIEW  INTEL PENTIUM D 920 , INTEL PENTIUM D 930

INTEL PENTIUM D 920 , INTEL PENTIUM D 930  6800XT REVIEW

6800XT REVIEW  computer hardware REVIEW

computer hardware REVIEW  INTEL CONROE CORE DUO 2 REVIEW VS AMD AM2

INTEL CONROE CORE DUO 2 REVIEW VS AMD AM2  INTEL PENTIUM D 805 INTEL D805

INTEL PENTIUM D 805 INTEL D805  Free desktop wallpaper

Free desktop wallpaper  online fighting game

online fighting game  Xtreview price comparison center

Xtreview price comparison center Lastest 15 Reviews

Rss Feeds

Last News

- The new version of GPU-Z finally kills the belief in the miracle of Vega transformation

- The motherboard manufacturer confirms the characteristics of the processors Coffee Lake

- We are looking for copper coolers on NVIDIA Volta computing accelerators

- Unofficially about Intels plans to release 300-series chipset

- The Japanese representation of AMD offered monetary compensation to the first buyers of Ryzen Threadripper

- This year will not be released more than 45 million motherboards

- TSMC denies the presentation of charges from the antimonopoly authorities

- Radeon RX Vega 64 at frequencies 1802-1000 MHz updated the record GPUPI 1B

- AMD itself would like to believe that mobile processors Ryzen have already been released

- AMD Vega 20 will find application in accelerating computations

- Pre-orders for new iPhone start next week

- Radeon RX Vega 57, 58 and 59: the wonders of transformation

- ASML starts commercial delivery of EUV-scanners

- The older Skylake processors with a free multiplier are removed from production

- Meizu will release Android-smartphone based on Helio P40

- AMD Bristol Ridge processors are also available in American retail

- The fate of Toshiba Memory can be solved to the next environment

- duo GeForce GTX 1080 Ti in GPUPI 1B at frequencies of 2480-10320 MHz

- New Kentsfield overclocking record up to 5204 MHz

- Lenovo released Android-smartphone K8

HALO 3 HALO 3 - Final Fight!

PREY Prey is something you don t often see anymore: a totally unigue shooter experience.

computer news computer parts review Old Forum Downloads New Forum Login Join Articles terms Hardware blog Sitemap Get Freebies