OOPS! You forgot to upload swfobject.js ! You must upload this file for your form to work.

Intel talked about the architectural features of processors Core M Broadwell

![]()

|

xtreview is your : Video card - cpu - memory - Hard drive - power supply unit source |

|

|||

|

|

||||

Recommended : Free unlimited image hosting with image editor

Recommended : Free unlimited image hosting with image editor

|

POSTER: computer news || INTEL TALKED ABOUT THE ARCHITECTURAL FEATURES OF PROCESSORS CORE M BROADWELL |

DATE:2014-09-14 |

|

|

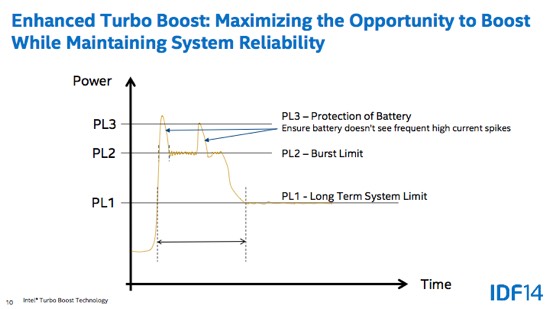

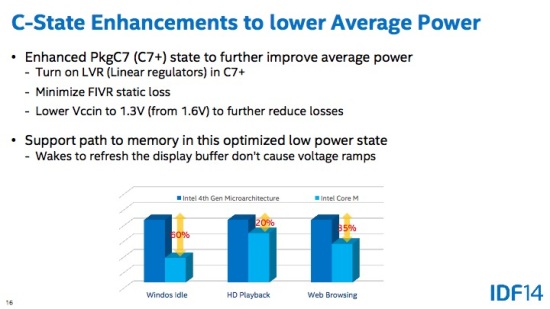

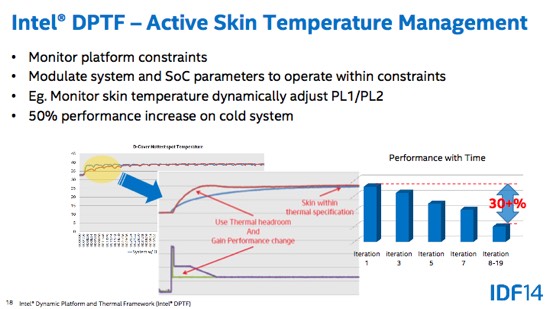

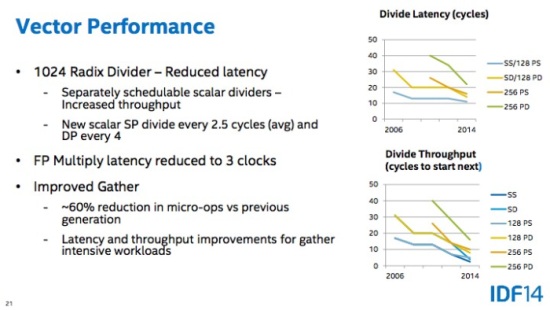

Intel's own event for developers, held twice a year, traditionally focused solutions for future generations. Visitors IDF demonstrated engineering samples of processors, and specially trained people broadcast about the most significant changes in their architecture. At this time Intel told about Broadwell processors generation , which belong to the line of Core M. Core M processors have increased energy efficiency, in this context, a lot of changes is connected with power management. Firstly, there is a threshold to two power PL1 (for long-term use) and PL2 (peak level that the system can use a very short time) added PL3 - the maximum permissible level, limited protection from overcharging the battery.  Secondly, was improved integrated into the processor voltage regulator (FIVR). In particular, there were linear regulators to work in the states C7 + ultra-low power consumption.   Third, there is support for throttling cycles per chip PCH, which, incidentally, is part of a package together with directly by the CPU Core M and is manufactured in 22-nm technology. Intel shows that it also saves energy.  Separately, Intel said that the "cold" processors will have higher performance, with the difference in efficiency can reach 50%.  In the computational part of the processors also changed. In particular, the number of records scheduling order execution has increased from 60 to 64 pieces, from 1000 to 1500 entries increased TLB (page 4 KB and 2 MB), added a new buffer pages to 1 GB on 16 records. Increased performance in vector computations.  Related Products : | ||

|

|

||

|

xtreview is your : Video card - cpu - memory - Hard drive - power supply unit source |

|

|

|

|

||

|

Xtreview Support  N-Post:xxxx Xtreview Support        |

INTEL TALKED ABOUT THE ARCHITECTURAL FEATURES OF PROCESSORS CORE M BROADWELL |

| Please Feel Free to write any Comment; Thanks  |

Intel and Samsung have talked about the prospects for EUV-lithography (2017-03-01)

Intel talked about the performance of Cannonlake processors (2017-02-10)

The creators of the State of Decay 2 talked about the size of the game world (2016-12-07)

Vampyr developers talked about the game (2016-11-17)

Experts have talked about Radeon RX 480 overclocking potential (2016-07-14)

AMD talked about some features of Polaris (2016-05-18)

AMD talked about their contribution to the development of virtual reality technology (2016-03-15)

AMD talked about the new display technology (2015-12-09)

Steve Jobs talked about the creation of car in 2008 (2015-11-05)

Samsung talked about flexible AMOLED-display second generation (2015-04-26)

Intel talked about the geography of their enterprises (2015-04-03)

Micron talked about applications processors Automata (2015-01-23)

Intel talked about the architectural features of processors Core M Broadwell (2014-09-14)

Jonathan talked about new materials in future Apple products (2014-06-18)

Razer talked about the project and modular PC Christine smart bracelet Nabu (2014-06-13)

Apple chief designer talked about his work and attitude to competitors (2014-03-18)

Intel has talked about a new graphics architecture (2014-02-12)

AMD once again talked about the availability of Kaveri processors (2013-09-11)

AMD talked about the server plans for 2014 (2013-06-18)

Google head talked about patent disputes (2013-05-16)

![]()

To figure out your best laptops .Welcome to XTreview.com. Here u can find a complete computer hardware guide and laptop rating .More than 500 reviews of modern PC to understand the basic architecture

7600gt review

7600gt is the middle card range.

We already benchmarked this video card and found that ...

geforce 8800gtx and 8800gts

geforce 8800gtx and 8800gts  Xtreview software download Section

Xtreview software download Section  AMD TURION 64 X2 REVIEW

AMD TURION 64 X2 REVIEW  INTEL PENTIUM D 920 , INTEL PENTIUM D 930

INTEL PENTIUM D 920 , INTEL PENTIUM D 930  6800XT REVIEW

6800XT REVIEW  computer hardware REVIEW

computer hardware REVIEW  INTEL CONROE CORE DUO 2 REVIEW VS AMD AM2

INTEL CONROE CORE DUO 2 REVIEW VS AMD AM2  INTEL PENTIUM D 805 INTEL D805

INTEL PENTIUM D 805 INTEL D805  Free desktop wallpaper

Free desktop wallpaper  online fighting game

online fighting game  Xtreview price comparison center

Xtreview price comparison center Lastest 15 Reviews

Rss Feeds

Last News

- The new version of GPU-Z finally kills the belief in the miracle of Vega transformation

- The motherboard manufacturer confirms the characteristics of the processors Coffee Lake

- We are looking for copper coolers on NVIDIA Volta computing accelerators

- Unofficially about Intels plans to release 300-series chipset

- The Japanese representation of AMD offered monetary compensation to the first buyers of Ryzen Threadripper

- This year will not be released more than 45 million motherboards

- TSMC denies the presentation of charges from the antimonopoly authorities

- Radeon RX Vega 64 at frequencies 1802-1000 MHz updated the record GPUPI 1B

- AMD itself would like to believe that mobile processors Ryzen have already been released

- AMD Vega 20 will find application in accelerating computations

- Pre-orders for new iPhone start next week

- Radeon RX Vega 57, 58 and 59: the wonders of transformation

- ASML starts commercial delivery of EUV-scanners

- The older Skylake processors with a free multiplier are removed from production

- Meizu will release Android-smartphone based on Helio P40

- AMD Bristol Ridge processors are also available in American retail

- The fate of Toshiba Memory can be solved to the next environment

- duo GeForce GTX 1080 Ti in GPUPI 1B at frequencies of 2480-10320 MHz

- New Kentsfield overclocking record up to 5204 MHz

- Lenovo released Android-smartphone K8

HALO 3 HALO 3 - Final Fight!

PREY Prey is something you don t often see anymore: a totally unigue shooter experience.

computer news computer parts review Old Forum Downloads New Forum Login Join Articles terms Hardware blog Sitemap Get Freebies